SOI (Silicone on Insulator) wafers were introduced in 1978 as an alternative technology due to their high speeds, error-reduction, low power usage, improved scaling and their immunity to latch-up. Originally, SOI processes were used in small niche markets, but these applications have broadened to the mainstream markets over the years. SOI wafers are now widely used in microprocessors, servers and RF signal processors as well as in college or university test research.

Typically, when we talk silicon on insulator wafers or SOI wafer fabrication there are two main methods used. The first involves implantation of oxygen into the silicon wafer. The other entails bonding two wafers thermally then separating them so that a thin layer of silicon is transferred between them. Several other more intricate and advanced fabrication methods have evolved out of the second technique.

Since silicon wafers are predominantly used in the manufacturing of micro-electro-mechanical systems or (MEMS) technology, their performance capabilities, cost and size are the three main considerations for buyers. The end product for most of these applications goes to the retail environment, so finding lower cost solutions in the SOI wafer fabrication process is essential to provide compact devices with high performance at lower manufacturing costs.

The demand for lower cost wafers in production is driving huge advancements with manufacture of these tiny components.

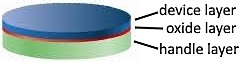

SOI wafers are manufactured by bonding

two silicon wafers together, having an

insulating oxide between. Devices are

built on the active layer.

The main appealing factor of SOI wafer technology is that it has an insulating layer that shields the micro device. For this application, they are created using materials in three layers. The first is known as the device layer which consists of a thin film of high-quality silicon where transistors are located. The second is made of silicon dioxide and it isolates the transistors from the third layer. The latter is made of bulk silicon and its role is to provide structural support. Depending on the intended application, a SOI wafer can either be thin or thick-filmed, at almost any thickness needed.

As mentioned earlier, the main advantage is that they enable the manufacture of smaller devices. The manufacturing process optimizes the efficiency of transistors and allows chips to be packed close together, resulting in a greater yield per wafer. As consumers continue to demand compact devices, designers strive to come up with chips that have the ability to hold more information in a small space. This facilitates the use of flexible designs that have greater potential.

Though their cost exceeds that of their bulk silicon counterparts, the additional features offered by SOI wafers reduce the expenses incurred in manufacturing advanced products. They can also be made with pre-etched cavities to simplify the manufacturing process and reduce the time needed for development. They also make it possible to produce chips of high quality without having to use expensive equipment. As their application spectrum continues to broaden, their prices are also decreasing substantially.

SOI wafers make it possible to create products of superior quality. The insulating layer minimizes leakage of electrical current. This in turn decreases power consumption while improving performance. The amount of heat dissipated also reduces, which enables MEMS to be applied in high-temperature environments with no adverse effects.

Signal noises are also blocked by the insulating layer. This results in greater transistor switching speed which in turn improves accuracy of the product. In a nutshell, SOI wafers are greatly improving the fabrication of MEMS, thus opening an avenue for new applications and products. The more experience MEMS foundries have in creating these wafers, the faster and more affordable they become, making this fabrication technique for silicone wafers more and more commercially appealing.

Jessica is a founder of Rogue Valley Microdevices, providing custom SOI wafer fabrication and free quotes for SOI wafers and MEMS services.

More Computer Architecture Articles:

• The Microcontroller Memory Map

• Digital to Analog Convertion with a Microcontroller

• CPU Process Memory Address Binding

• First-Come, First-Served CPU Scheduling Algorithm

• The Microcontroller Interrupt System

• Operating System Services

• Basic Electronics for Computer Architecture

• The AMD Athlon 64 X2 Processor

• Logical Versus Physical Memory Addresses

• The Motherboard Chipset