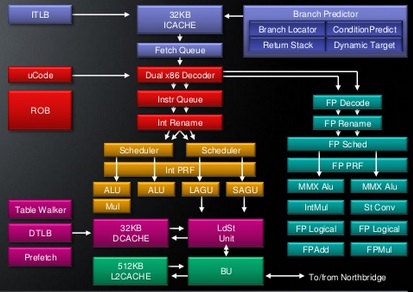

Bobcat Microarchitecture

AMD's Bobcat (codename) microarchitecture was released in early 2011 to serve the low-power/low-cost market. It uses 40 nm (nanometer) die technology and has a power dissipation of 18 Watts.

Bobcat microarchitecture. Image source AMD.

Bobcat features:

• 64-bit core

• Out-of-order execution

• Advanced branch predictor

• Dual x86 instruction decoder

• 64-bit integer unit with two ALUs

• Floating-point unit with two 64-bit pipes

• Single channel 64-bit memory controller

• 32KB instruction cache

• 32KB data L1 cache

• 512KB L2 cache

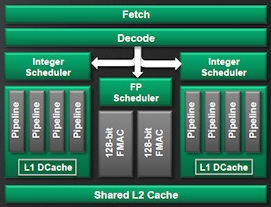

Bulldozer Microarchitecture

AMD's Bulldozer (codename) microarchitecture was released in October of 2011, to replace the K10 microarchitecture. It uses 32 nm (nanometer) Silicon on insulator (SOI) process technology and has a power dissipation of 125 watts.

Bulldozer microarchitecture. Image source AMD.

Bulldozer microarchitecture uses dual-core "modules". Each module has 2 MB of L2 cache 16 KB 4-way of L1d (way-predicted) cache 64 KB of 2-way L1i cache, two ALU (Arithmetic Logic Unit), two AGU (Address Generation Unit), and two symmetrical 128-bit FMAC (fused multiply–add capability) floating-point pipelines.

All modules share the L3 cache as well as an Advanced Dual-Channel Memory Sub-System (IMC - Integrated Memory Controller).

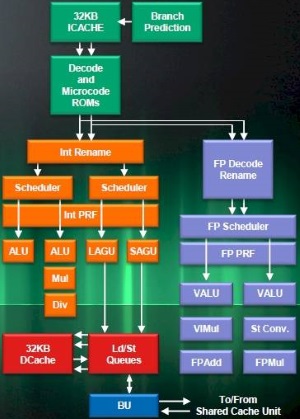

Jaguar Microarchitecture

AMD's Jaguar (codename) microarchitecture was released in mid 2013 as an improvement to the Bobcat microarchitecture. It was designed for tablets, notebooks, and embedded applications like PlayStation Xbox. It uses 28 nm (nanometer) die technology and has a power dissipation of 6 Watts.

Jaguar microarchitecture. Image source AMD.

Jaguar features:

• 32 KiB instruction + 32 KiB data L1 cache

• 16 way, 1-2 MiB unified L2 cache shared by two or four cores

• Out-of-order execution and Speculative execution

• Integrated memory controller

• Two-way integer execution

• Two-way 128-bit wide floating-point and packed integer execution

• Integrated Fusion controller hub chipset

More Computer Architecture Articles:

• Electronic Circuits

• Learn Assembly Language Programming on Raspberry Pi 400

• Intel's Sandy Bridge Micro-Architecture

• Microcontroller's Parallel I/O System

• Microcontrollers

• ARM Cortex-A72 Registers

• Multiuser Operating System Functions

• CPU Chip Packaging

• AMD's Phenom Processor

• Multithreaded Programming Process' and Threads