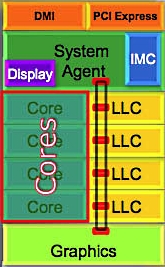

"Sandy Bridge" is Intel's code name for a new cpu core microarchitecture. It's based on the 32nm "Westmere" microarchitecture, which is a die shrink of the 45nm "Nehalem" microarchitecture, but introduces a few new or improved features. In Sandy Bridge, the memory controller, the PCI Express (PCIe) controller, and video circuitry are all located within the processor die and so can share data more easily than previous microarchitectures. The new "ring architecture" Sandy Bridge uses a cache (called Last Level Cache (LLC)) between the CPU and graphics cores.

Sandy Bridge introduces Turbo 2.0 which improves the performance of Turbo Boost. Turbo Boost is a technology to temporaly overclock the chip, but overclocking causes the chip to run hotter. Previously Turbo Boost discontinued when the core reached its maximum design temperature. Turbo 2.0 allows the chip to operate beyond the maximum design temperature for 20 seconds because after that short interval the chip's temperature can be brought down within safe limits. Turbo 2.0 can overclock the cpu core, the graphics core, or both.

Sandy Bridge's Quick Sync Video is an improvement in video which accelerates encoding with fixed-function logic working in concert with the co-processor, and decoding by moving the complete decode pipeline to an efficient fixed-function multi-format codec. Another new feature in Sandy Bridge are the Advanced Vector Extensions (AVX), new microcodes that improve floating point–intensive appliction performance.

The Sandy Bridge microarchitecture will be used in Intel's second generation of Core i3⁄i5⁄i7 processors using a new socket type. The new LGA1155 socket has the retention notches in a different location. You can't plug a Sandy Bridge processor into an older LGA1156 socket motherboard.

More Computer Architecture Articles:

• The Motherboard Chipset

• Intel's Core 2 Processors

• Operating System Memory Page Sharing

• Intel Celeron D Processor

• Processor Affinity in Symmetric Multiprocessing

• Analog to Digital Convertion with a Microcontroller

• Operating System Process Management

• Logical Versus Physical Memory Addresses

• How Computer Chips are Made

• Basic Decoder Circuitry